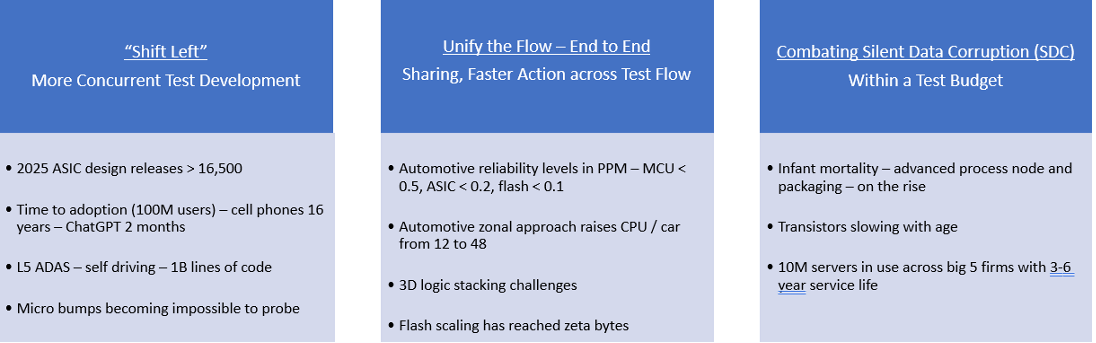

Is semiconductor device test non-value included? Definitely, some elements are unvarying. Test is just one of the 3 methods to ensure components in enhancement to characterization and the layout itself. Provided the marketplace background– throughout automobile, computer, and progressed product packaging– brand-new test difficulties and worth includes have actually arised. 3 major styles are “shift left”, which is the demand for even more simultaneous growth with ever-increasing dependences in between layout, product packaging, test, and area procedure; better marriage in growth, manufacturing, and throughout the end-to-end test circulation; and the ongoing battle on quiet information corruption (SDC)– stabilized with test business economics (Number 1).

What is Change Left?

The term “Shift Left” has actually been made use of progressively within growth to show jobs that were when carried out sequentially yet should currently be done simultaneously. This is typically because of tightening up dependences in between jobs. A number of sorts of “design for…” techniques are holding as devices within a more comprehensive layout for test (DFT) umbrella: S (tension), R (dependability), I (examination), and O (observability). Past test, some automobile companies are utilizing S (safety) and S (security).

In easier items wafer probe was an appropriate methods for identifying Understood Great Pass away (KGD) as a gross display prior to setting up. Currently there is much excessive worth in an 8 FET SiC component [1] or 2.5/ 3D calculate multichip components such as system-in- plan (SiP) and chiplets. The probe has to create as near to KGD as feasible. With numerous types of innovative product packaging, all the interconnects should be examined despite ease of access– therefore the term understood excellent pile (KGS) and on the whole understood excellent system (KGS).

The Universal Chiplet Interconnect Express (UCIe) spec [2], focused on die-to-die, has actually been updated to 1.1 attending to even more procedures and more comprehensive use versions. As 3D pass away piling develops from high-bandwidth memory (HBM) memory to reasoning, there are brand-new difficulties specifically when utilizing reasoning from different procedure nodes. One instance is brand-new physical tension systems and a greater chance of adjoin failings.

The IEEE 1838 spec for die-to-die heaps is an additional instance of a “shift left” in bringing layout and test better. KGx begins with the design and item preparation, requires to be sustained by the layout, and is supplied by test and setting up procedures.

Extra complicated test circulations and much more costly bill-of-material (BoMs) call for better marriage throughout the end-to-end test circulation for growth and activity in manufacturing.

Automated test devices (ATE) and system-level test (SLT) affiliation reveals a massive rise in the demand for SLT after ATE test. SLT can be as high as 50-100x less costly than ATE, yet it traditionally has actually been an “island” running really various and lengthy (assume 20 mins) formulas reflective of end consumer usage situations.

Intel notes that a lot of its consumers run SLT for a lot longer durations than the business does. Numerous advancements by Teradyne and Advantest promote much more feed-forward and comments of test patterns from both atmospheres to make preliminary test growth outcomes in boosted response times to boost upstream ATE test when brand-new failing settings show up at SLT. Various other instances consist of doing much more analytics on the tester on the fly.The advantages of this consist of flexible examinations. As an example, if a provided set of product (wafers, ended up products) is showing particular parametric around procedure edges (fast/slow transistors, high/low power) after that the test program can be adaptively and dynamically differed. ATE manufacturers have actually positioned even more of these devices within the tester for real-time decision-making, instead of a main test flooring computer system.

At IEEE ITC in October 2023, Cariad (the electronic devices arm of Volkswagen) explained that screening for ADAS L4 and L5 atmospheres produces a great deal of information that, presently, is a missed out on chance for analysis/action. The marriage of ATE examinations would certainly remove the overlap and replication that originate from exactly how test was traditionally done, with batteries of examinations from silos of R&D, quality control, safety, and product/test/design companies.

Can We Remove Silent Information Corruptions?

All these advancements in screening and marriage behave– yet why are really refined, quiet information corruptions (SDC) still taking place in the area? Is the solution much more screening? They are quiet and also if the device is found, after that added screening includes expenditure.

At IEEE ITC 2023, there was an exceptional panel conversation on SDC regarding exactly how to capture them in production, do innovative flaw versions, boost testing, and the advantages of telemetry. Generally, 2 major reasons were highlighted: Great antique arbitrary factors flaws and even more systemic parametric kind failings within complicated layouts.

The factor flaws can be time absolutely no test runs away or abandons that simply call for a little of ‘activation’ time to arise. Can much more “intelligent” high voltage examinations be conjured up? The much more threatening instances, although parametric in nature, include really little hold-up results and/or voltage sags under complicated power systems and circumstances. It asks the concern– can much more be done in design/validation to cover correct IC work? Extra particularly, if a component is stated to be “pass” or “fail”, after that the whole problem established requirements to be comprehended ie: at what regularity at what voltage? A multi-layer strategy is required. Should quiescent present testing/fingerprinting be restored? However besides these initiatives– will we just locate the simple systems and the tough ones will remain to thwart us?

In recap, the sector chauffeurs, such as automobile, calculate, and progressed process/package nodes; incorporated with the endless mission to be smaller sized, much better, much faster, and more affordable– remain to result in brand-new test difficulties. Even More “shift left” is required in test to accelerate and boost the top quality of growth. Criteria such as IEEE 1838 and UCIe 1.1 are actions in the ideal instructions. Greater marriage is taking place throughout the test procedure circulation, consisting of connecting SLT and consumed test much more carefully, and relocating even more ‘on the fly’ analytics to the tester for real-time response. Last but not least, SDC gets on the increase and is really difficult in a cost-efficient way.

[1] “SiC MOSFET Challenges, Demand and Industrialization of Test & Burn-in”– Mark Berry, 3D InCites, [2] “Update on UCIe”– Mark Berry, 3D InCites, October 2022November 2022

This post initially showed up in the 2024 3D Prompts Yearbook.

![It was all going well until… | Squid Game 2 | Netflix [ENG SUB] It was all going well until… | Squid Game 2 | Netflix [ENG SUB]](https://thehollywoodpremiere.com/wp-content/uploads/2025/01/It-was-all-going-well-until-Squid-Game-2-120x86.jpg)