NIST held the “Chiplet Interfaces Technical Standards Workshop” at the NIST National Cybersecurity Facility of Quality in December 2023.

Throughout this workshop, technological specialists from market, academic community, standards-setting companies, and market partnerships collected to review and focus on certain standards initiatives connected to chiplet-based styles with a concentrate on physical and rational interfaces, intending to drive development in the semiconductor and microelectronics market.

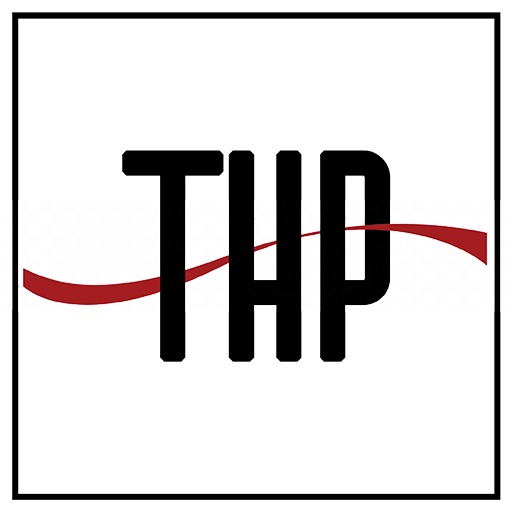

Allow’s very first have a look at what locations the common standards teams are operating in.

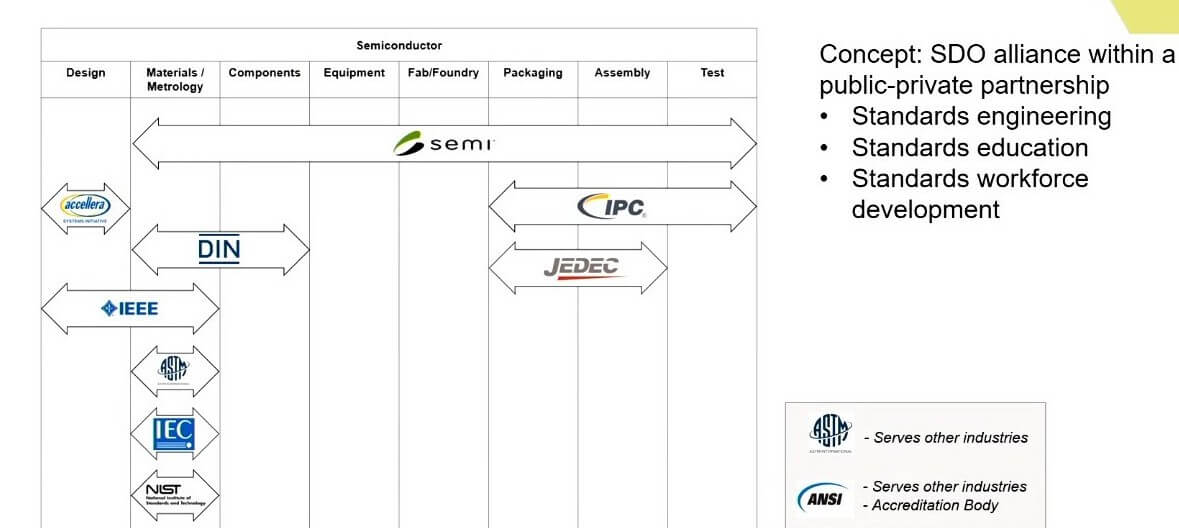

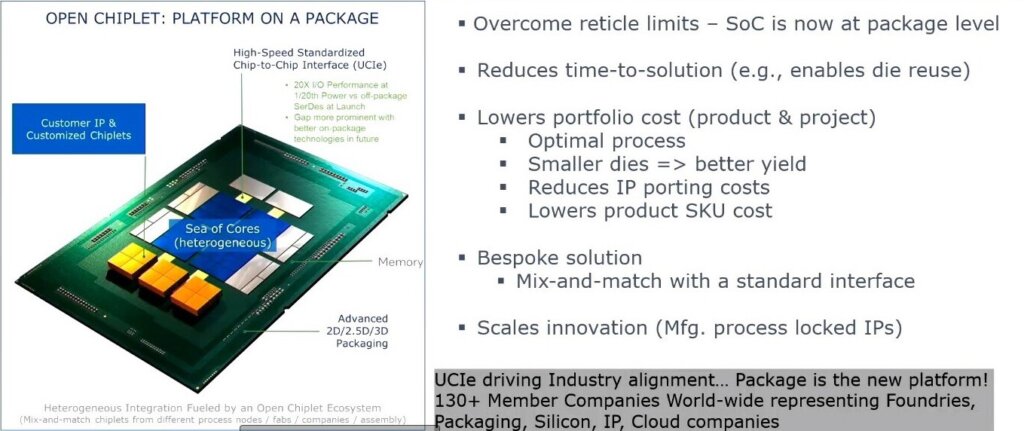

Debendra Das Sharma, Intel Sr Other and co-inventor and chairman of the UCIe chiplet adjoin basic shared his input on what is currently the leading chiplet market criterion.

In Sept of 2023, Intel disclosed the examination chip “Pike Creek” having an Intel UCIe chiplet made on IFS Intel 3, a Synopsys UCIe IP chiplet made utilizing the TSMC N3E procedure node and packaged utilizing Intel EMIB technology.

This effective pairing imitates the blending and matching of passes away that can happen in real-world multi-die chiplet components, showing that this strategy is readily feasible. Intel’s strategies to change from exclusive interfaces to the UCIe user interface in its next-generation Arrowhead Lake customer cpus additionally emphasize the value of this innovation (Number 2).

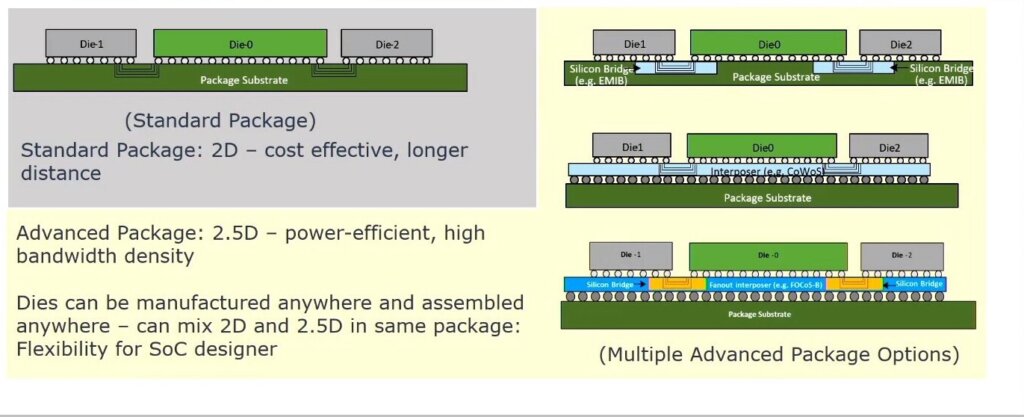

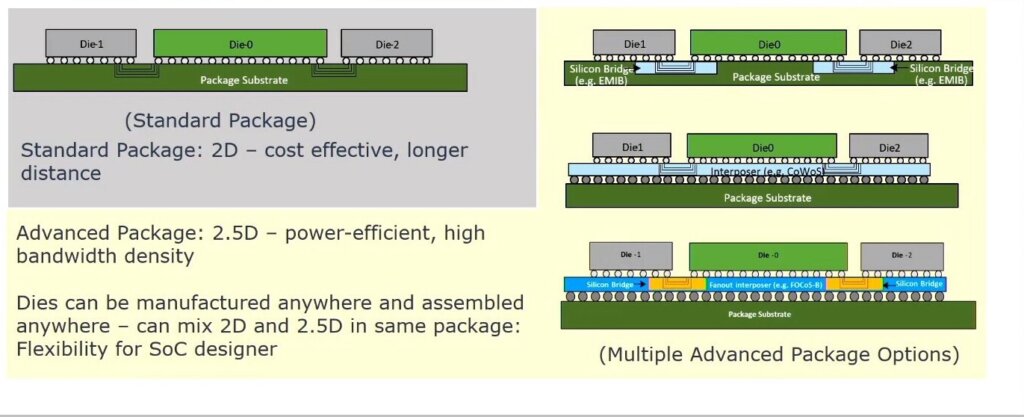

UCIE sustains both basic and innovative plans as received Number 3.

Dr. Sreejit Chakravarty whose job consists of placements at Intel, LSI, and Avago presently chairs the IEEE P3405 job team on Chiplet Interconnect Examination and Repair work, which intends to systematize the examination and fixing of chiplet interconnects.

This criterion specifies efficient and reliable devices to examine and fix chiplet interconnects. The basic consists of the following:

A Design interpretation for the examination and fixing of chiplet interconnects. The design includes the list below components: chiplet adjoin clustering, collection clocking and redundancy, collection fixing muxing and mux re-configuration assistance, lane numbering, and fixing trademark style. Additionally, the criterion specifies screening assistance for high-volume production of chiplet interconnects.

A summary language that specifies the examination and fixing equipment, the trademark style, the message style for interaction in between both passes away and the die designs made use of for confirming the examination facilities.

Table 1: Attribute, attribute pattern, and examination ramifications for chiplet user interface standards.

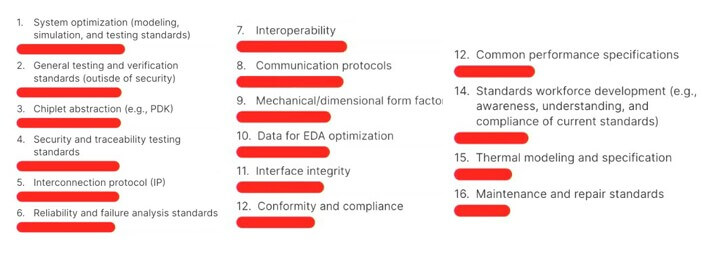

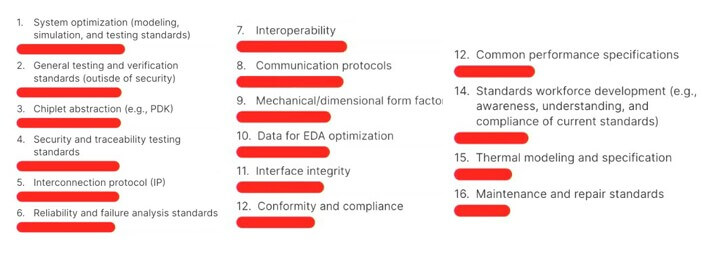

The Majority Of Day 2 was occupied by participants prioritizing what standards require to be dealt with. The last prioritization listing, made a decision by participants, is received Number 4.

Samsung To Establish Chip Product packaging Study center in Japan

Samsung revealed that it will certainly spend around $280MM over 5 years in constructing a center for innovative chip product packaging research study in Japan’s Kanagawa prefecture near Yokohama.

Japan apparently will give Samsung aids worth approximately 20 billion yen as it seeks to sustain the revitalization of residential chip production. Samsung apparently currently has a r & d facility neighboring and felt this action would certainly grow connections with Japanese tools and products providers.

For every one of the current on Advanced Product packaging remain connected to IFTLE … … … … …

![Iyanya, Mayorkun & Tekno – ‘One Side’ (Remix) [Official Music Video] Iyanya, Mayorkun & Tekno – ‘One Side’ (Remix) [Official Music Video]](https://thehollywoodpremiere.com/wp-content/uploads/2024/11/Iyanya-Mayorkun-Tekno-One-Side-Remix-Official-Music-120x86.jpg)